Pengendalian daya statis selalu menjadi tantangan bagi para insinyur dalam desain elektronik portabel. Terutama pada aplikasi seperti power bank dan power bank all-in-one, meskipun IC kontrol utama masuk ke mode tidur, arus bocor kapasitor masih terus mengonsumsi energi baterai, sehingga menyebabkan fenomena "konsumsi daya tanpa beban", yang sangat memengaruhi masa pakai baterai dan kepuasan pengguna terhadap produk terminal.

- Analisis Teknis Akar Penyebab -

Inti dari arus bocor adalah perilaku konduktif kecil dari media kapasitif di bawah pengaruh medan listrik. Besarnya dipengaruhi oleh banyak faktor seperti komposisi elektrolit, keadaan antarmuka elektroda, dan proses pengemasan. Kapasitor elektrolit cair tradisional rentan terhadap penurunan kinerja setelah perubahan suhu tinggi dan rendah atau penyolderan reflow, dan arus bocor meningkat. Meskipun kapasitor solid-state memiliki keunggulan, jika prosesnya tidak canggih, masih sulit untuk menembus ambang batas level μA.

- Keunggulan Solusi dan Proses YMIN -

YMIN mengadopsi proses jalur ganda yaitu “elektrolit khusus + pembentukan presisi”

Formulasi elektrolit: menggunakan bahan semikonduktor organik dengan stabilitas tinggi untuk menghambat migrasi pembawa muatan;

Struktur elektroda: desain penumpukan multi-lapisan untuk meningkatkan area efektif dan mengurangi kekuatan medan listrik per unit;

Proses pembentukan: Melalui peningkatan tegangan secara bertahap, lapisan oksida padat terbentuk untuk meningkatkan tegangan tahan dan resistansi kebocoran. Selain itu, produk ini tetap mempertahankan stabilitas arus kebocoran setelah penyolderan reflow, sehingga memecahkan masalah konsistensi dalam produksi massal.

- Deskripsi Verifikasi & Keandalan Data -

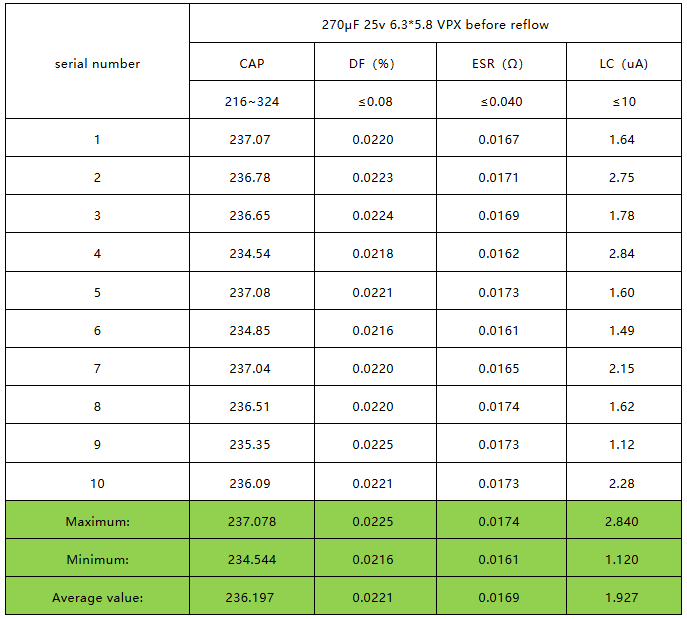

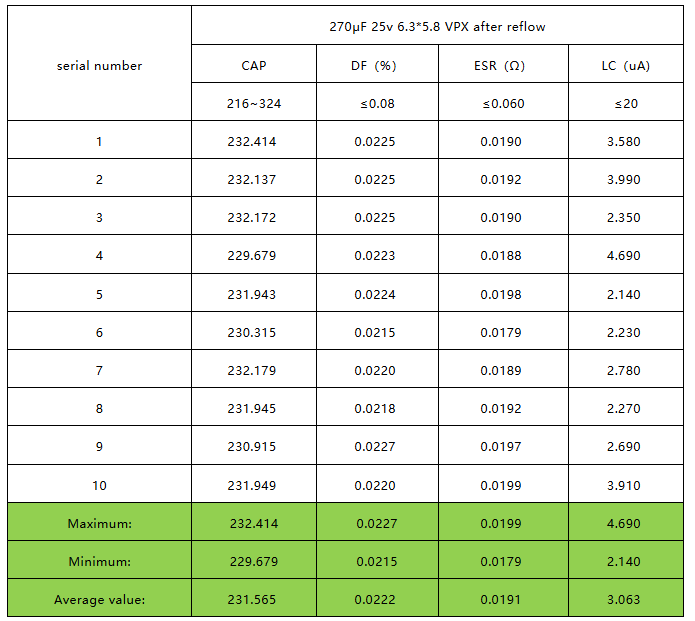

Berikut ini adalah data arus bocor spesifikasi 270μF 25V sebelum dan setelah penyolderan reflow (satuan arus bocor: μA):

Data uji pra-reflow

Data uji pasca-reflow

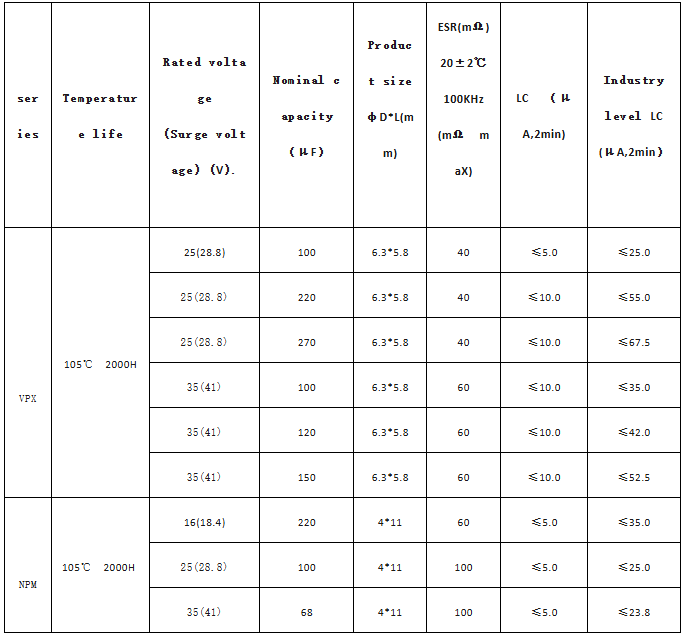

- Skenario Aplikasi dan Model yang Direkomendasikan -

Semua model stabil setelah penyolderan reflow dan cocok untuk jalur produksi SMT otomatis.

Waktu posting: 13 Oktober 2025